从物理的角度来看,总线(BUS)是一组传输公共信号线的集合,是传输地址、数据和控制信号的公共通路,由一组导线和相关的控制(协议)驱动电路组成。

总线

总线的基本概念:

从物理的角度来看,总线(BUS)是一组传输公共信号线的集合,是传输地址、数据和控制信号的公共通路,由一组导线和相关的控制(协议)驱动电路组成。

在主板上安装有若干个插槽,允许插入各个模块(CPU板、存储器板和I/O板等)。主板上的印制电路线将各插槽的相应点连接起来,即为总线。

总线标准

指芯片之间、扩展卡之间以及系统之间,通过总线进行连接和传输信息时,应该遵守的一些协议和规范。

接口标准

外设接口的规范,涉及接口信号线定义、信号线传输速率、信号传输方向和拓扑结构,以及电气特性和机械特性等多个方面。

总线和接口的区别

- 总线标准具有公用性;接口标准大多是专用的;

- 总线往往以主板上的总线扩展槽形式提供使用;接口一般是以接口插座(头)形式提供使用。

- 总线一般是并行传输;接口有并行传输,也有串行传输。

- 总线定义的信号线多,且齐全,有分离的控制总线、数据线和地址线;接口的信号线少,而且不齐全,一般是控制线、数据线和地址线共用。

如今,总线和接口的区别越来越小,尤其是总线串行化趋势使总线和接口更加难以区分

总线特性

- 物理特性:指总线的物理连接方式,包括总线的根数,总线的插头、插座的形状,引脚线的排列方式等。(以便于设计者进行设计)

- 功能特性:描述总线中每一根线的功能

- 电气特性:定义每一根线上信号的传递方向及有效电平范围。送入CPU的信号叫输入信号(IN),从CPU发出的信号叫输出信号(OUT)

- 时间特性:定义了每根线在什么时间有效。规定了总线上各信号有效的时序关系,CPU才能正确无误地使用

总线的主要性能参数

- 总线频率:MHz表示的工作频率,是总线频率的一个重要参数。

- 总线宽度:指数据总线的位数

- 总线的数据传输率:总线的数据传输率=(总线宽度/8位)*总线频率

总线分类

- 按总线结构分:

- 单总线:所有模块都连接到单一总线上。单总线具有结构简单便于扩充等优点。但是由于所有数据的传送都通过这一共享的总线,在此处可能成为计算机的瓶颈。

- 双总线\三总线:将速度较低的I/O设备从总线上分出去,而形成系统总线与I/O总线分开的双总线结构。根据同一思想,可以组成三总线结构。在系统总线和扩展总线之间增加一条高速总线,将图形、视频和网络等连到高速总线上,而慢速I/O设备仍连到扩展总线。

- 按功能和信号传输类型:数据传送线、仲裁总线、中断和同步线、公用线(现代总线结构)

- 数据传送线:

- 地址总线:假如为32位(A31~A0)。可寻址的内存单元为232=4GB( 约等于 42.9 亿字节)。计算机的I∕O接口也是通过地址总线来寻址的。地址总线是单向的,寻址总是由 CPU 发出的。

- 控制总线:CPU 到存储器和外设接口的控制信号,如:存储器请求 MREQ、I/O 请求、IORQ、读信号 RD、写信号 WR 等等。由外设送到 CPU 的信号,如 8086 中的 READY 以及 INT 等。

- 数据总线:如 32 位数据线(D31 ~ D0)。可以表示 0 ~ 231-1(无符号数)或 –231-1 ~ 231-1(有符号数)。由于数据在 CPU 与存储器和 CPU 与 I∕O 接口之间的有输入、输出两种操作,所以数据总线是双向的。可以传输的信息:数值数据、指令、设备码、控制字、状态字。

- 数据传送线:

- 按总线的层次分:

- CPU总线(内部总线):微机系统中速度最快的总线,主要在CPU内部,连接CPU内部各部件。

- 局部总线:在系统总线和CPU总线之间的一级总线,提供CPU和主板器件之间以及CPU到高速外设,之间的快速信息通道。

- 系统总线:也成为I/O总线,通过总线扩展卡连接外部设备的总线。

- 通信总线:也成为外部总线,是微机与微机,微机与外部设备(如打印机、硬盘设备)、仪器仪表之间的通信通道。

总线标准

芯片、扩展卡与系统之间通过总线连接和通信时,应当遵循的协议和规范。

总线的负载能力

负载能力:指当总线接上负载后必须不影响总线输入/输出的逻辑电平。

总线输出驱动能力

- 输出低电平时,吸收了负载电流后,仍能保持低电平

- 输出高电平时,输出了负载电流后,仍能保持高电平

总线输入对插线板的影响:插线板负载

- 输入低电平时,总线向插线板灌电流

- 输入高电平时,吸收插线板的电流

增强总线负载能力的一般方法:

- 在总线和负载间加接缓冲器或驱动器,常用三态缓冲器,其作用是驱动和隔离。(在板卡,即适配器上带有缓冲驱动器,或在接口芯片内部有缓冲驱动器单元)

XT、ISA总线

XT总线

PC/XT总线是将 CPU的引脚经过8282锁存器、8286发送接收器、8288总线控制器、8259中断控制器、8237DMA控制器以及其他逻辑电路的重新驱动和组合控制而形成的。

总线信号线安排:共62条

8条双向数据线D7D0 ;A0 ;

20条单向地址线A19

控制线:

6条中断请求线;

3对DMA申请线和4条DACK线;

4条 存储器和I/O设备的读写命令线;

1条系统时钟信号线、1条I/O奇偶检测线、

1条I/O就绪线及其他联络信号线。

4种电源(±5V、 ± 12V)共8条线。

执行一条I/O指令的过程:

- 指令周期:不同指令的指令周期是不等的。一个指令周期由一个或若干个总线周期组成。

- 总线周期:CPU通过总线与外部进行信号输入、输出交换信息所需的时间

- 时钟周期:时钟脉冲的重复周期。可见时钟周期是CPU的时间基准。又叫T状态。

基于XT总线接口设计所需要的主要总线信号:

- 地址信号A15-A0

- 数据总线信号D7-D0

- 控制总线信号-IOR,-IOW,AEN

ISA总线

ISA(Industry Standard Architecture,工业标准体系结构)是IBM PC/AT(80286)机上首先使用,故又称为AT总线,后被国际标准化组织确定为国际标准ISA.

ISA(Industrial Standard Architecture,工业标准体系结构)总线起源于IBM-PC微型计算机的出现

ISA插槽由基本的62线8位插槽和扩展的36线插槽两部分组成

ISA信号说明

- 数据线D0~D15:双向三态

- 低位地址线A0~A19:输出,可寻址1MB,带锁存

- 高位地址线LA17~LA23:输出,寻址范围16MB,不带锁存,A19~A17不复用,提高数据传输率

- 地址锁存允许信号ALE:输出,高电平有效

- 中断请求信号IRQ2

IRQ7、IRQ10IRQ14:输入,上升沿有效 - 地址使能信号AEN:输出,高电平有效。高电平表示DMA周期。CPU控制总线时,该信号保持低电平

- I/O读信号IOR#:输出,低电平有效

- I/O写信号IOW# :输出,低电平有效

- 存储器读 MEMR#:输出,低电平有效

- 存储器写MEMW#:输出,低电平有效

- 数据总线高字节使能 SBHE# :输出,低电平有效

- 16位I/O片选信号I/OCS16#:输入,低电平有效

- 16位存储器片选MEMCS16#:输入,低电平有效

PCI总线

PCI总线(Peripheral Component Interconnect,外围部件互连总线)于1991年由Intel公司首先提出,并由PCI SIG(Special Interest Group)来发展和推广。由于PCI总线先进的结构特性及其优异的性能,使之成为现代微机系统总线结构中的佼佼者,并被多数现代高性能微机系统所广泛采用。

PCI特点

66MHz时钟,峰值传输速率为264MBytes/s,适合告诉数据传输的要求。

突发传输模式,确保总线数据不断地处于满载状态

独立于CPU工作,PCI是独立于处理器总线标准,通过主桥路和处理器相连,与不同的处理器相连不影响PCI设备的使用

自动配置功能:每个PCI设备上都有256字节的配置空间支持:PCI设备的即插即用

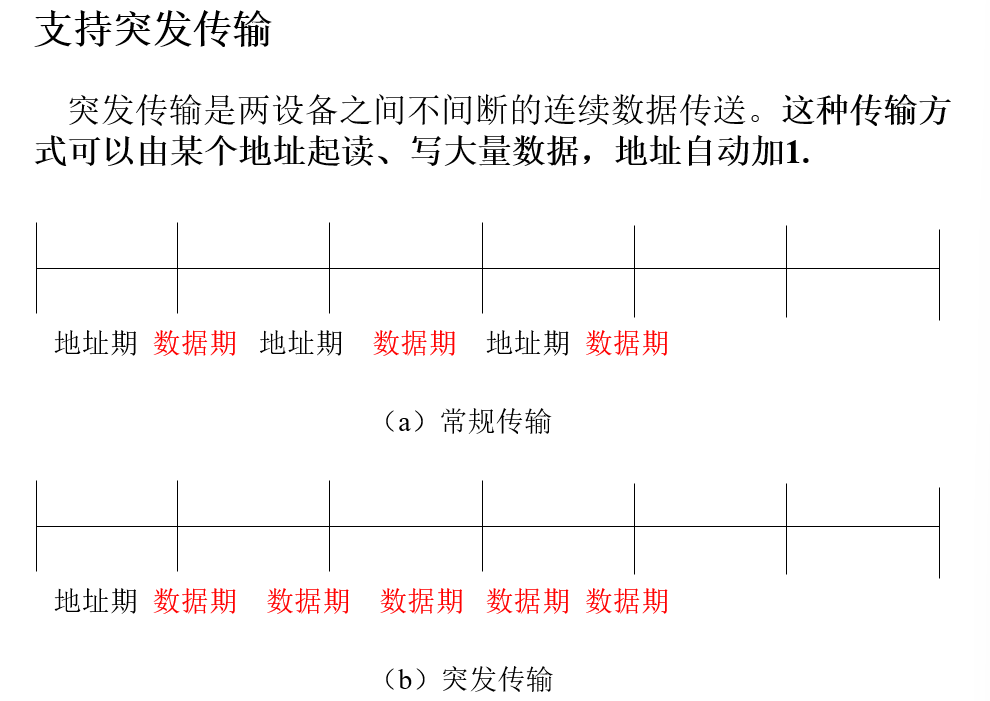

支持突发传输:突发传输是两设备之间不间断的连续数据传送。这种传输方式可以由某个地址起读、写大量数据,地址自动加1

PCI插槽和PCI扩展卡:

- PCI总线规范定义了5V和3.3V两种工作电源电压

- 连接器有32位和64位两种

- 5V的连接器用于3.3V时,需要旋转180度

- PCI接口卡的金手指根据需要可设计成5V通用、5V/32位、5V/64位以及3.3V通用、3.3V/32位、3.3V/64位等多种形式

PCI总线接口信号:

- 线号类型说明:

- IN:表示输入信号

- OUT:表示输出信号

- T/S:表示双向三态I/O信号

- S/T/S:表示持续的低电平有效的三态信号。

- O/D:表示漏极开路,以线或方式允许多个设备共享

PCI地址空间

PCI总线三种独立的地址空间:内存地址空间、I/O地址空间和配置地址空间

配置空间是PCI所特有的一个物理空间。由于PCI支持设备即插即用,所以PCI设备不占用固定的内存地址空间或I/O地址空间,而是由操作系统决定其映射的地址。

系统加电时,BIOS检测PCI总线,确定所有连接在PCI总线上的设备以及它们的配置要求,并进行系统配置

所有的PCI设备必须实现配置空间,从而能够实现参数的自动配置,实现真正的即插即用。

内存地址空间和IO地址空间是80x86体系原有的。配置地址空间是PCI特有的,用于PCI的·硬件资源配置。即插即用,板卡设置配置空间寄存器,系统启动时,BIOS读出参数,系统动态分配地址。

地址译码方式

- PCI总线的每个设备都有自己的地址译码逻辑

- 支持正向、负向两种地址译码方式

- 正向译码:每个设备都监视地址总线上的访问地址是否落在它的地址范围内

- 负向译码:未被其它设备在正向译码中接受的所有译码要等总线上其它所有设备都拒绝之后才能确定,总线上只能有一个设备采用此种方式。如标准扩展总线。

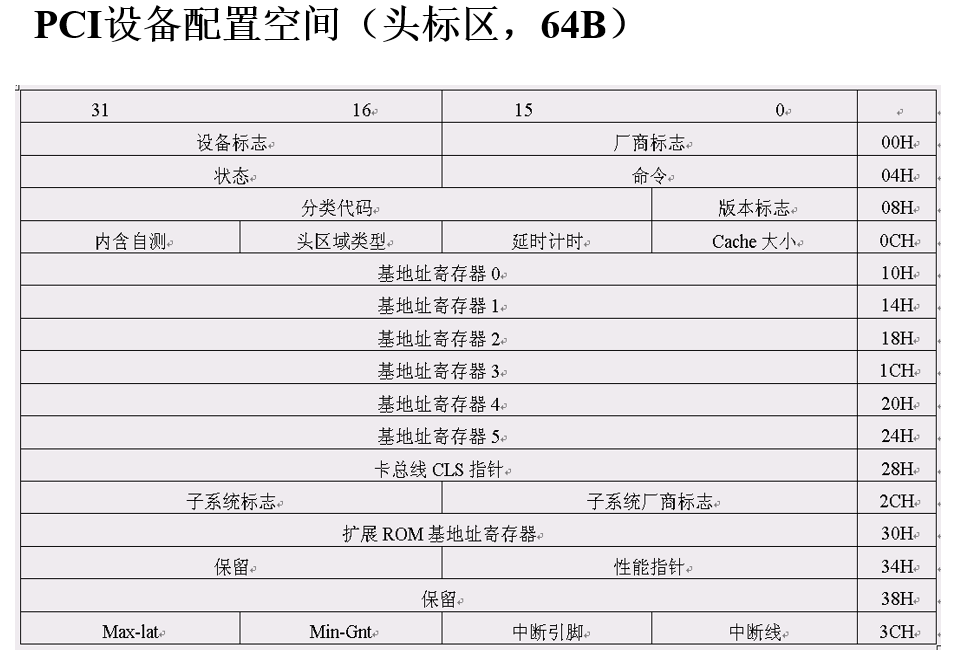

PCI配置空间

一个物理PCI设备可能包含多个功能块(简称功能)

一个设备的所有功能(总线标准规定最多8个功能)共用一个IDSEL信号;

每个功能均有一个配置空间

配置空间大小256B(64个双字),其中头区域大小为64B

配置空间的访问(获得配置信息)

- 在系统上电时,BIOS及操作系统配置软件扫描系统的各条总线,以确定总线上存在什么设备以及它们需要什么配置

- 配置软件读取设备的配置寄存器·(配置读操作总线周期)

- 确定设备所需地址空间

- 分配中断以及主设备对总线的访问要求等

PCI-Express概述

简称PCI-E,或PCIe。是PCI总线的发展。与PCI的主要不同是物理连接不同;通信模型及程序方法采用分层协议。

USB总线

传统的接口电路,每增加一种设备,就需要为它准备一种接口或插座,还要为它们准备各自的驱动程序。这些接口插座各不相同,给使用和维护带来了困难。USB是英文Universal Serial Bus缩写,即通用串行总线。其采用通用的连接器,使用热插拔技术,使得外部设备的连接使用大大简化,收到了普遍的欢迎,已经成为了流行的外围I/O总线。

USB特点

- 速度快:USB 1.1传输速率12Mbps,USB 2.0传输速率480Mbps

- 连接简单快捷:直接连接,无需关机、重新启动、打开机箱等操作

- 无需外接电源:USB提供内置电源,能向低压设备提供5V的电源

- 支持多连接:USB支持多设备连接,

- 良好的兼容性:USB接口标准有良好的向下兼容性

- 低功耗

USB系统的硬件

(1)USB主控制器/根集线器(Host Ctrl/Root Hub)

- 由主控制器和根集线器组成-

- 主控制器:连接到PCI总线。可作为主设备通过PCI总线直接与MEM交换数据;

- 功能:实现并-串转换、创建USB事务、管理USB事务传输过程(在根集线器与主机MEM间传递结果)。占用一定数量I/O地址空间,受CPU控制。

(2)USB集线器(USB Hub)

- 由控制器和中继器组成,最多支持4个USB端口;

- 有高速(支持USB2.0)和全速(USB1.x)2种类型;

- 可集成在USB设备内部,不作为独立硬件出现。

- 每个USB HUB占用一个USB逻辑地址;

- 每个USB HUB具有一定数量(≤16)的USB端点。

(3)USB设备

- 可分为HUB设备(USB集线器)和功能设备两种。

- 功能设备类型:有高速、全速或低速三种类型。

- 每个USB设备占用一个USB逻辑地址;

- 每个USB设备具有一定数量(≤16)的USB端点。

基本概念说明

- USB总线:由VCC、GND、D+、D-四根线组成,D+和D-通过差分方式作为一根数据线(半双工)使用

- USB事务:USB总线上最基本的一次数据交换操作

- USB逻辑地址:逻辑地址不通过连线实现;

- 每个USB集线器和USB设备(不连接到PCI总线),均不占用I/O地址空间(无I/O地址),只具有一个惟一的USB逻辑地址(USB系统自动配置所分配);

- USB端口:连接USB总线的连接器;

- USB端点:集线器或设备的内部寄存器(仿照I/O端口起名,又要与USB端口区分),编号在0~15之间。